At this week’s Hot Chips 2023 event, Arm unveiled its Arm Neoverse Compute Subsystems (CSS) offering, which promises to simplify and accelerate the adoption of Arm Neoverse technology into new solutions. It’s a powerful enabler that will reduce the friction of integrating Arm IP into new designs and accelerate the time-to-market for Arm’s partners.

News: Arm’s CSS Subsystem Approach to Processor Development

Neoverse CSS provides a customizable compute subsystem configured, validated, and optimized by Arm, reducing cost, risk, and time-to-market for partners developing specialized silicon. CSS N2 lets Arm’s partners focus on SoC and system-level innovation, saving time and resources.

It supports domain-specific accelerator integration, including AI, and excels in performance per watt for cloud-native workloads. Arm CSS N2 is already available and proven in silicon, marking a milestone for Arm in making custom silicon accessible and speeding up time-to-market.

The Arm Neoverse Compute Subsystems (CSS) enable partners to build specialized silicon more affordably and quickly than discrete IP solutions. The first-generation CSS product, Arm CSS N2, is based on the Neoverse N2 platform, optimized for performance and efficiency on a 5nm process. CSS N2 provides partners with a customizable compute subsystem, fostering innovation in memory, IO, acceleration, and more.

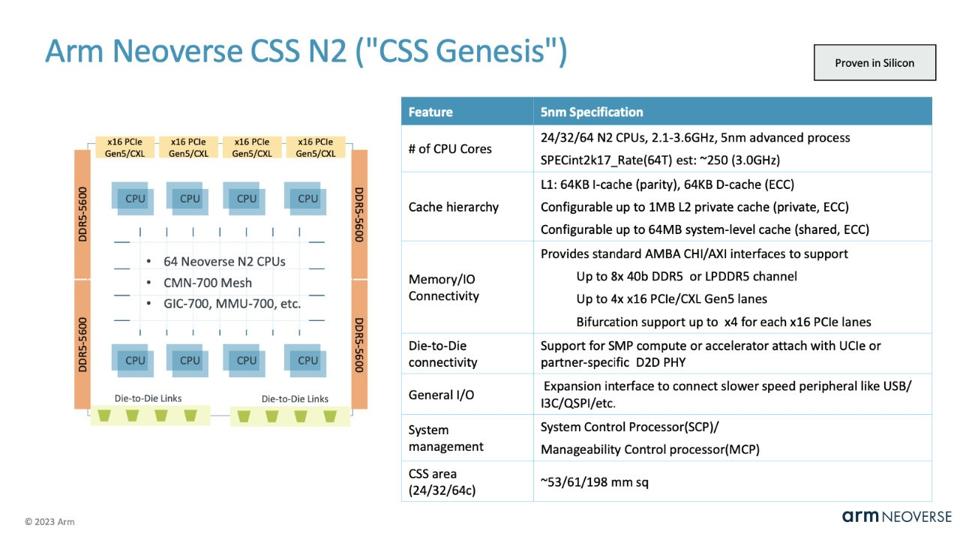

Neoverse CSS N2 offers configurable core counts (24, 32, or 64 cores), with core frequencies ranging from 2.1GHz to 3.6GHz, all implemented using advanced 5nm process technology. Each N2 core supports Armv9 instructions for vector processing and ML, enhanced cryptography, memory partitioning, monitoring, and power management, making CSS N2 suitable for various applications from 5G to Cloud Computing and ML.

CSS N2 is compatible with the latest memory and I/O technologies, supporting up to 8x 40b DDR5 or LPDDR5 channels per die, and up to 4x x16 PCIe/CXL combo PHYs and controllers, each with 4-way bifurcation down to 4x x4 lanes.

Neoverse CSS N2 offers multi-core and multi-chip scaling capabilities, supporting up to 256 cores across two sockets and facilitating high-speed chip-to-chip links to cater to diverse cloud-to-edge use cases. The design supports on-die and externally attached accelerators, allowing for on-chip accelerators through Arm’s NI-700 network-on-chip interconnect or off-chip acceleration via PCIe Gen5/CXL1.1 PHYs.

Arm Neoverse CSS N2 incorporates essential compute subsystem elements, including system control and management handled by embedded Cortex-M7 processors. The System Control Processor (SCP) manages system functions like clock control and power domains. At the same time, the Manageability Control Processor (MCP) interfaces with an external BMC for management, RAS, event logging, and communication alerts.

CSS N2 is SystemReady SR certified (SystemReady is Arm’s compliance certification program) and includes a reference firmware stack and virtual fixed platform model. This allows partners to efficiently develop platform firmware, integrate OS and services, and optimize boot flows, security, and power management before final silicon tape-out.

Analysis

Arm CSS N2 will provide significant commercial and technical advantages for its partners. By relieving the complexity of developing the compute subsystem, Arm’s customers can focus on specialized computing to meet data challenges while promoting sustainability and reducing power consumption. Several Arm processor vendors have already incorporated CSS N2-based silicon and are witnessing impressive results.

Arm told us that one partner saved over eighty engineering years of integration work, while spent only 13 months from kick-off to working silicon. In an industry where processor development efforts can take up to three years of efforts, even with large development teams, this is compelling.