Last week I did an advisory session the current state of the memory and NAND market, which is experiencing a marked upturn driven by constrained supply of legacy DRAM products and surging demand from artificial intelligence infrastructure builds.

Legacy and mobile DRAM types, including DDR4 and LPDDR5X, face severely extended delivery lead times, while contract prices for DRAM and NAND flash are rising sharply. This is leaving Smartphone OEMs and SoC vendors with elevated memory cost burdens that threaten margins and will likely force higher device prices.

Here I’m sharing the notes I used for that discussion. Enjoy,.

Current Situation (November 2025)

| Segment | Q4 2025–H1 2026 Trend | Key Drivers |

|---|---|---|

| DDR4 / LPDDR4X | 🔺 Severe shortage, +20–30% prices | Supply cuts, HBM shift |

| DDR5 / LPDDR5X | 🔺 Rising 15–30% QoQ | AI servers, smartphones |

| HBM | 🔺 High now, potential ↓ in 2026 | Yield improvement, competition |

| NAND / eMMC / UFS | 🔺 5–11% increase | AI storage growth, plant disruptions |

| QLC SSDs | 🔺 Explosive growth by 2026 | Data-center demand, HDD shortages |

Delivery Lead-Time Expansion

- Orders for LPDDR5X memory now carry lead times of 26–39 weeks, meaning inventory placed today may not arrive until mid-2026.

- OEMs report strained supply for both DRAM and NAND modules, creating procurement challenges across product lines.

Contract Price Increases

- Major memory suppliers, including Samsung Electronics and SK hynix, raised DRAM and NAND flash contract prices by up to 30% for Q4 2025.

- Market indices show DRAM contract prices rising approximately 16% month-on-month for certain configurations, with DRAM price escalations of 15-20% in Q4 and NAND increases of approximately 10%.

Supply Reallocation & Production Constraints

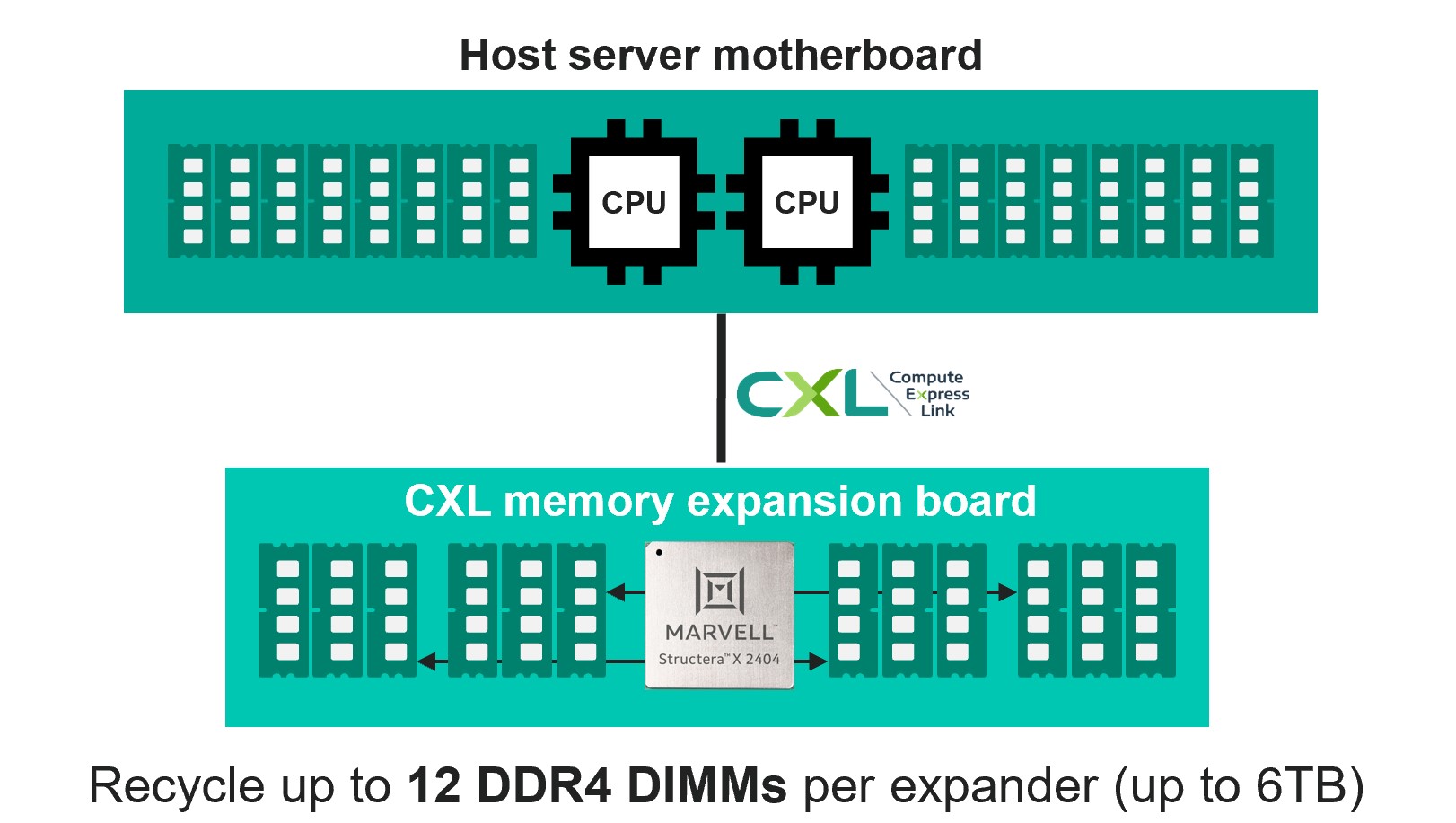

- Memory manufacturers are diverting capacity from mature DRAM nodes (e.g. DDR4 and LPDDR4) toward higher-margin products including HBM and DDR5.

- Legacy-node DRAM output is declining significantly, with forecasts indicating DDR4 production may fall to approximately 20% of 2025 levels in 2026.

- The wafer capacity consumed by HBM exceeds that of standard DRAM by a factor of three, increasing the opportunity cost of legacy DRAM production.

Demand Drivers

- AI server infrastructure and inference workloads are driving memory expansion across HBM, DDR5 RDIMM, and LPDDR5X.

- On-device AI and mobile memory growth (12+ GB configurations becoming standard in smartphones) are pushing up memory content per unit.

- Stockpiling and long-term supply arrangements are gaining traction, with major OEMs and data-center operators reportedly locking in 2–3 year memory contracts.

Impact on Smartphone OEMs and SoC Vendors

- Standard smartphones now typically include 12 GB DRAM modules in their bill of materials, with high-end configurations exceeding this baseline. Memory cost increases therefore materially affect device economics.

- Xiaomi cited memory cost surges as a principal driver for higher retail pricing of its recent device launch.

- MediaTek faces cost pressure from both rising memory prices and foundry costs, with 2nm wafer cost escalations beginning in Q4 2025.

Memory Segment Dynamics

DRAM and Legacy Nodes

- DDR4 and LPDDR4X node production is shrinking as manufacturers prioritize new-node DRAM and HBM.

- Spot and contract prices for DDR4 modules have reportedly doubled year-over-year in certain channels.

- With supply constrained and inventories low, OEMs must secure allocation earlier, reducing flexibility in production planning.

High-Bandwidth Memory (HBM)

- HBM commands higher margins than commodity DRAM.

- Twelve-layer HBM4 chips are expected to fetch approximately $500 each, compared with roughly $300 for the predecessor HBM3e generation.

- Although HBM remains a smaller volume market compared with commodity DRAM, its superior margins are driving capacity reallocation decisions.

NAND Flash

- NAND contract prices rose approximately 10% in Q4, responding to SSD demand spikes from AI and data-center deployments and HDD supply constraints.

- High-stack 3D NAND and QLC SSD segments are seeing accelerated procurement ahead of device launches in 2026.

Competitive & Strategic Implications

For Memory Suppliers

- Memory suppliers benefit from elevated DRAM and NAND average selling prices and improved utilization of mature-node fabs.

- Long-term contracts lock in pricing and shift negotiation power toward suppliers. However, potential oversupply risk exists in HBM as next-generation node transitions (including HBM4) ramp up and could depress pricing in 2026.

For SoC Vendors and OEMs

- SoC vendors such as MediaTek may experience margin compression if memory cost inflation cannot be passed fully to device manufacturers.

- Smartphone OEMs face a difficult choice between higher retail pricing—potentially impacting volume—and reduced margins.

- Mid- and low-end segments are especially vulnerable to cost spikes, as higher memory content in devices tightens cost control.

- Device manufacturers may accelerate product-mix shifts toward higher-margin models or constrain DRAM and flash content growth to offset cost increases.

For Data-Center and AI Infrastructure Providers

- AI infrastructure builders face higher memory component costs, especially for server DRAM, HBM stacks, and large-capacity NAND. This may increase total system cost per accelerator or per data-center node.

- Memory supply constraints may create vendor lock-in, favoring large players who secure long-term deals while smaller customers face allocation disadvantages.

Competitive Threats

- Suppliers in Taiwan, including Nanya Technology, Winbond, and Powerchip Technology, stand to gain from elevated legacy DRAM pricing and supply shifts.

- Emerging Chinese memory producers such as ChangXin Memory Technologies could accelerate plant ramp-up, threatening incumbents’ market share if pricing declines or capacity slack emerges.

Outlook & Risk Considerations

- The memory sector appears to be in a sustained upward phase (a “supercycle”) with several analysts projecting elevated prices into at least the first half of 2026.

- The primary risk lies in oversupply: as memory makers ramp next-generation HBM4 and DDR5 capacity and yield improves, pricing pressure may emerge, particularly for HBM stacks.

- Some forecasts expect double-digit HBM price declines in 2026.

- Buyers that locked long-term contracts may mitigate cost exposure, but inventory risk and deferred delivery lead times create execution risk for OEMs and system integrators.

- Ecosystem players must weigh product launch timing and potential margin erosion against premium device positioning and cost inflation.

Bottom Line

- Extended lead times and significant price increases across DRAM and NAND flash underscore a structural shift in the memory supply chain.

- Device OEMs and SoC vendors face immediate margin pressure or must raise selling prices—both of which affect competitiveness.

- Memory chip suppliers gain increased negotiating power and improved profitability but must manage the transition to next-generation technologies and avoid a sharp down-cycle.

- Data-center and AI infrastructure providers now face higher memory component costs per system, which may impact deployment economics.

- Competitive threats are escalating from regional players gaining share and from emerging capacity that could unwind the current price rally.

- The memory pricing environment tightens strategic dynamics across the semiconductor ecosystem and raises the bar for costRetry

Background: Market Size & Segment Trends

| Metric | Value / Trend |

|---|---|

| Combined DRAM + NAND market size (2025) | ~ US$191.5 billion globally |

| CAGR | ~ 8.4% from 2025 toward 2034 ( |

| Technology transition: NAND layering | >176-layer 3D NAND in 2024; >200-layer expected by 2026 |

| Technology transition: DRAM generation & premium segments | DDR5/LPDDR5X adoption rising; server DRAM and HBM demand growing; legacy types facing supply pull-back. |

| Regional and supply concentration | Asia-Pacific (led by South Korea) dominates >50% of global memory output. |

| Demand segmentation | AI/Datacentre → growing fastest; Consumer/mobile/PC → more moderate growth or even softness in some segments. |

Raw Notes on per-Supplier Situation

| Supplier | Memory/NAND Type | Reported Yield / Capacity / Technology Issues | Strategic Implications / Risk |

|---|---|---|---|

| Samsung Electronics | HBM4 / “1c” DRAM node for high-bandwidth memory | • Reports that Samsung delayed mass production of HBM4 to 2026 due to yield issues. • Rumoured yields for “1c” DRAM for HBM4 as low as ~50 % early on. • Yet there are recent claims of “90% logic die yield” for HBM4 from Samsung. • End-of-life shift: Samsung and others phasing out older DRAM/NAND nodes (e.g., DDR4) and reallocating capacity. | • Because of yield/yield ramp issues, Samsung may lag in delivering high-end HBM4 volumes, giving advantage to competitors. • For buyers, parts from Samsung may carry premium or have longer lead times until maturity is established. • The discrepancy in reported yield (50% vs 90%) suggests risk: early reported 90% may cover logic die only; full stack yield may still be lower. • If Samsung delays production, supply for HBM among fewer suppliers may tighten further — implications for systems reliant on HBM. |

| SK hynix | NAND flash (3D NAND, 321-layer etc) & HBM4 | • SK hynix has ramped 321-layer NAND flashes into mass production. • SK hynix says its 4-D NAND tech (horizontal source connection) reduced defect rates and improved productivity for their 238-layer and 321-layer NAND. • In HBM4: SK hynix says it is “readying” HBM4 production after internal certification. | • SK hynix appears to be in a stronger position for new generation NAND and HBM; fewer ramp/yield issues publicly reported, which may give it competitive advantage. • For procurement: capacity from SK hynix may be more reliable or earlier available for high-end memory/NAND stacks. • However, this early advantage also means SK hynix may command premium pricing or prioritise high-end customers, leaving others behind. |

| Micron Technology | DRAM (DDR5, next-gen nodes) & HBM | • Micron introduced DDR5 on a “1γ” node process (EUV-based) for its DDR5 devices. • Reports indicate next-gen DRAM node transitions (1α/1β/1γ) may face yield drop initially: “As fabs migrate to 1β and 1α nm nodes … yields can initially drop.” • Micron has faced supply/demand shifts: for example, shifting away from certain legacy nodes (DDR4) which implies capacity shifts. Public note: Micron issued DDR4 EOL for PC/data centre customers. | • The node transition risk means that DRAM from Micron (or others) may face higher cost, longer ramp time, or possible yield-issues, impacting availability. • For memory module/system builders relying on Micron’s latest DRAM, need to check qualification/maturity; early batches might carry higher risk or cost. • On the flip side, Micron’s early move to next-gen may give it advantage once yields stabilise, but near term could be supply-constrained. |

| Other/Regional Suppliers (e.g., ChangXin Memory Technologies (CXMT), China) | DRAM (DDR5) | • CXMT reportedly delayed mass production of DDR5 chips to late 2025 due to thermal stability issues and yields ‘just above 50%’. | • While not yet a major global supplier, this shows that yield risk is high for newer entrants or for new nodes especially in DRAM. • For system builders sourcing globally, this implies risk if relying on alternative/new suppliers — need strong validation and contingency. |